# RAGE<sup>TM</sup>128 Software Development Guide

# Technical Reference Manual P/N: SDK-G04000 Rev 0.01

© 1999 ATI Technologies Inc.

### **CONFIDENTIAL MATERIAL**

All information contained in this manual is confidential material of ATI Technologies Inc. Unauthorized use or disclosure of the information contained herein is prohibited.

You may be held responsible for any loss or damage suffered by ATI for your unauthorized disclosure hereof, in whole or in part. Please exercise the following precautions:

- Store all hard copies in a secure place when not in use.

- Save all electronic copies on password protected systems.

- Do not reproduce or distribute any portions of this manual in paper or electronic form (except as permitted by ATI).

- Do not post this manual on any LAN or WAN (except as permitted by ATI).

Your protection of the information contained herein may be subject to periodic audit by ATI. This manual is subject to possible recall by ATI.

The information contained in this manual has been carefully checked and is believed to be entirely reliable. No responsibility is assumed for inaccuracies. ATI reserves the right to make changes at any time to improve design and supply the best product possible.

#### ATI, mach64, PC2TV, 3D RAGE, and RAGE THEATER are

trademarks and/or registered trademarks of ATI Technologies Inc. All other trademarks and product names are properties of their respective owners.

## **Record of Revisions**

| Release | Date     | Description of Changes |

|---------|----------|------------------------|

| 0.01    | Aug 1999 | First draft completed. |

## **Related Manuals**

RAGE 128 Register Reference Manuals

# Table of Contents

### Chapter 1: Overview

| 1.1 | 1 Scope                                      |                |

|-----|----------------------------------------------|----------------|

| 1.2 | 2 Major Features of the RAGE 128             |                |

| 1.3 | 3 A Chapter Summary of this Manual           |                |

| 1.4 | 4 Notations and Conventions Used in this Mar | ual <i>1-4</i> |

| 1.5 | 5 Nomenclature and Conventions               |                |

|     | 1.5.1 Register and Field Names               |                |

|     | 1.5.2 Numeric Representations                |                |

|     | 1.5.3 Register Description                   |                |

### **Chapter 2: Programming Basics**

| 2.1 | Scope   |                                        | 2-1  |

|-----|---------|----------------------------------------|------|

| 2.2 | Overvie | PW                                     | 2-2  |

| 2.3 | Operati | on Modes                               | 2-4  |

|     | 2.3.1   | VGA Mode                               | 2-4  |

|     | 2.3.2   | Accelerator Mode                       | 2-5  |

| 2.4 | Drawin  | g Modes in Acceleration-operation Mode | 2-6  |

| 2.5 | Review  | of Imaging Terminology                 | 2-10 |

|     | 2.5.1   | Raster Image                           |      |

|     | 2.5.2   | True RGB Color                         |      |

|     | 2.5.3   | Representing Pixels                    |      |

|     | 2.5.4   | Pixels                                 | 2-14 |

|     | 2.5.5   | Pitch                                  |      |

|     | 2.5.6   | Video Memory                           |      |

| 2.6 | Memor   | y Apertures                            | 2-19 |

|     | 2.6.1   | VGA Memory Aperture                    | 2-20 |

|     | 2.6.2   | Video BIOS                             |      |

|     | 2.6.3   | Register Apertures                     |      |

|     | 2.6.4   | Linear Memory Apertures.               | 2-22 |

|     | 2.6.5   | AGP System Memory Image                |      |

|     | 2.6.6   | RAGE 128 PCI GART                      |      |

| 2.7 Display Mode and Mode Switching. | 2-27 |

|--------------------------------------|------|

| 2.8 Engine Discipline                |      |

| 2.9 BIOS Services                    |      |

# Chapter 3: Accelerator Operation Mode

| 3.1 | Scope   |                                                     |  |

|-----|---------|-----------------------------------------------------|--|

| 3.2 | Step 1: | Detect the RAGE 128                                 |  |

|     | 3.2.1   | Using the PCI Configuration Space                   |  |

|     | 3.2.2   | Scanning the BIOS Segment                           |  |

|     | 3.2.3   | Scratch Register Test                               |  |

| 3.3 | Step 2: | Obtain the Configuration Information                |  |

| 3.4 | Step 3: | Set a Display Mode                                  |  |

|     | 3.4.1   | Using the BIOS Function                             |  |

|     | 3.4.2   | Passing a CRT Parameter Table to Set a Display Mode |  |

|     | 3.4.3   | Manually Setting a Display Mode                     |  |

|     | 3.4.4   | Calculating the PLL Register Values                 |  |

|     | 3.4.5   | Determining the Post and Feedback Dividers          |  |

|     | 3.4.6   | Programming the DDA                                 |  |

| 3.5 | Step 4: | Initialize the GUI Engine                           |  |

# Chapter 4: Programming

| 4.1 | Scope                             | 4-1  |

|-----|-----------------------------------|------|

| 4.2 | Engine Command Queue Maintenance  | 4-2  |

| 4.3 | Programmed I/O Drawing Operations | 4-4  |

|     | 4.3.1 Drawing Rectangles          | 4-4  |

|     | 4.3.2 Drawing Lines               |      |

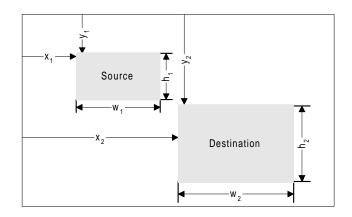

| 4.4 | Hardware Cursor                   | 4-19 |

# Chapter 5: CCE Engine Initialization and Usage

| 5.1 | Scope    |                                         | 5-1 |

|-----|----------|-----------------------------------------|-----|

| 5.2 | Starting | the CCE Microengine.                    | 5-3 |

|     | -        | Wait for Engine Idle                    |     |

|     | 5.2.2    | Load the Microcode into the Microengine | 5-3 |

|     | 5.2.3    | Load the CCE Registers                  | 5-4 |

|     | 5.2.4  | Cautions When Programming RAGE 128 in CCE Mode | 5-8  |

|-----|--------|------------------------------------------------|------|

| 5.3 | Ring B | uffer Management                               |      |

|     |        | The Ring Buffer Concept                        |      |

|     |        | Ring Buffer Server                             |      |

|     | 5.3.3  | Indirect Buffer                                | 5-15 |

|     |        |                                                |      |

### Chapter 6: CCE Packets

| 6.1 | Scope.  |                                      |  |

|-----|---------|--------------------------------------|--|

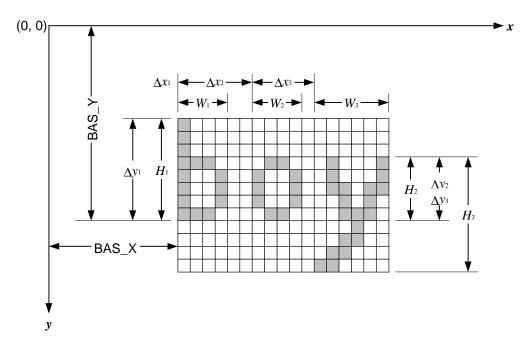

| 6.2 | 2D Coc  | rdinate System                       |  |

|     | 6.2.1   | Essentials of 2D Drawing Operations. |  |

| 6.3 | Drawin  | g Objects                            |  |

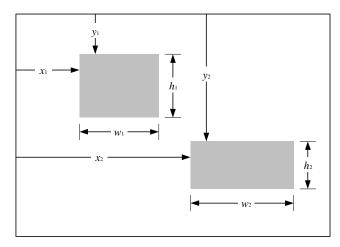

|     | 6.3.1   | Drawing Rectangles.                  |  |

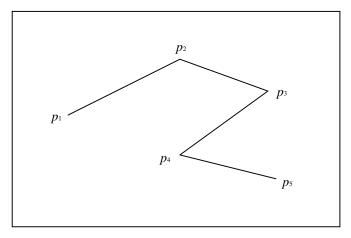

|     | 6.3.2   | Drawing Polylines                    |  |

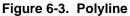

|     | 6.3.3   | Drawing Polyscanlines                |  |

| 6.4 | Block 7 | Fransfers                            |  |

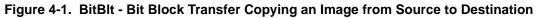

|     | 6.4.1   | Bit Block Transfer.                  |  |

|     | 6.4.2   | Transparent Bit Block Transfer       |  |

|     | 6.4.3   | Scaled Block Transfer                |  |

|     | 6.4.4   | Transparent Scaled Block Transfer    |  |

| 6.5 | Drawin  | g Text                               |  |

|     | 6.5.1   | Drawing Text in Small Font           |  |

|     | 6.5.2   | Drawing Text in Large Font           |  |

| 6.6 | 3D Ren  | dering                               |  |

|     | 6.6.1   | Setting Up the 3D Context            |  |

|     | 6.6.2   | Drawing 3D Primitives                |  |

|     | 6.6.3   | Texture Mapping.                     |  |

|     | 6.6.4   | Setting 3D Render States             |  |

### Chapter 7: Advanced Topics

| 7.1 | Scope  |                                                | 7-1  |

|-----|--------|------------------------------------------------|------|

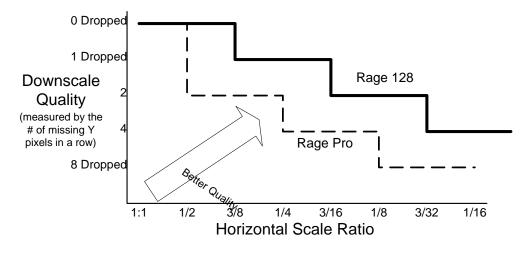

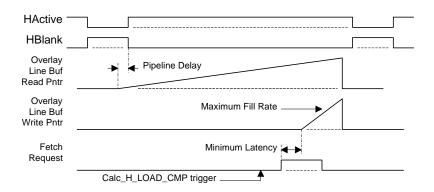

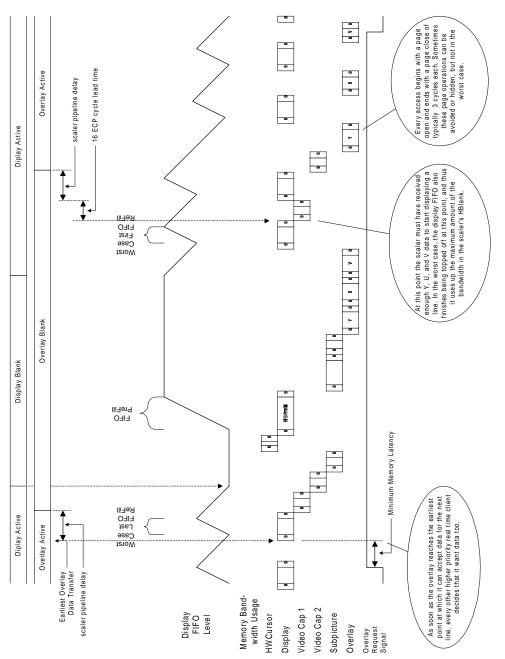

| 7.2 | Back-  | End Overlay and Scalar                         | 7-2  |

|     |        | Feature Summary for the Back End Video Scalar. |      |

|     | 7.2.2  | Functional Overview                            | 7-6  |

|     | 7.2.3  | Additional Quality Enhancements.               | 7-7  |

| 7.3 | Auto-  | Flipping and Advanced Deinterlacing            | 7-10 |

| 7.4 | Overla | ay Autonomous Updating                         | 7-12 |

| 7.5  |           | onizing Decoded Video Streams to the Display Refresh |      |

|------|-----------|------------------------------------------------------|------|

|      | 7.5.1     | GUI Stall Mechanism.                                 | 7-13 |

| 7.6  | Program   | nming the Scalar                                     | 7-15 |

|      | 7.6.1     | Overview                                             | 7-15 |

|      | 7.6.2     | Setup                                                | 7-15 |

|      | 7.6.3     | Bandwidth                                            | 7-15 |

|      | 7.6.4     | Managing Bandwidth                                   | 7-15 |

|      | 7.6.5     | Physical Scaling Ratios                              | 7-17 |

|      | 7.6.6     | Setting up the Horizontal Accumulator                | 7-17 |

|      | 7.6.7     | Setting up the Destination Window                    | 7-20 |

|      | 7.6.8     | Setting up the Source Window                         | 7-20 |

|      | 7.6.9     | Calculating the Filter Coefficients                  | 7-21 |

|      | 7.6.10    | Setting up the Vertical Accumulator                  | 7-23 |

|      | 7.6.11    | Autonomous Update                                    | 7-24 |

|      | 7.6.12    | Autoflipping and Advanced Deinterlacing.             | 7-25 |

| 7.7  | Color C   | Controls                                             | 7-28 |

| 7.8  | Keying    | Controls                                             | 7-29 |

| 7.9  | Tabulat   | ing Cycles in the HBlank                             | 7-30 |

|      | 7.9.1     | Part 1                                               |      |

|      | 7.9.2     | Part 2                                               | 7-31 |

|      | 7.9.3     | Part 3                                               | 7-32 |

| 7.10 | ) Tips fo | or Getting More Bandwidth                            | 7-35 |

| 7.1  | l Front-  | end Scalar                                           | 7-36 |

| 7.12 | 2 Bus M   | Iastering                                            | 7-37 |

|      | 7.12.1    | Bus Master Operation                                 |      |

|      | 7.12.2    | Creating a Descriptor Table                          |      |

|      | 7.12.3    | Setting up a System Bus Master Transfer              |      |

# Appendix A: BIOS Function Calls

| A.1 | Scope    |                                                       |

|-----|----------|-------------------------------------------------------|

| A.2 | AH = 0;  | Set Video Mode (AL = Video mode) <i>A-1</i>           |

| A.3 | AH = 1;  | Set Cursor TypeA-2                                    |

| A.4 | AH = 2;  | Set Current Cursor PositionA-2                        |

| A.5 | AH = 3;l | Read Current Cursor Position at the specified pageA-2 |

| A.6 | AH = 4;  | Read Current Light Pen PositionA-2                    |

| A.7 | AH = 5;  |                                                       |

| A.8 | AH = 6;  | Scroll Active Page UpA-3                              |

|                                                                             | AH = 7;   | A.9 A |

|-----------------------------------------------------------------------------|-----------|-------|

| Read Character/Attribute at Current Active Cursor PositionA-3               | AH = 8;   | A.10  |

| Write Character/Attribute at Current Cursor Position of a specified pageA-3 | AH = 9;   | A.11  |

| Ah;Write Character at Current Cursor Position of a specified pageA-4        | AH = 0Ah; | A.12  |

| Bh;Set Color PaletteA-4                                                     | AH = 0Bh; | A.13  |

| Ch;Write Dot (graphics mode)A-4                                             | AH = 0Ch; | A.14  |

| Dh; Read Dot (graphics mode)A-4                                             | AH = 0Dh; | A.15  |

| Eh; Write Teletype to Active PageA-4                                        | AH = 0Eh; | A.16  |

| Fh;Return Current Video SettingA-5                                          | AH = 0Fh; | A.17  |

| Dh;Set Palette RegistersA-5                                                 | AH = 10h; | A.18  |

| n; Character Generator RoutinesA-7                                          | AH=11h;   | A.19  |

| 2h; Return Current EGA Settings/Print Screen Routine SelectionA-9           | AH = 12h; | A.20  |

| 3h; Write String to Specified PageA-11                                      | AH = 13h; | A.21  |

| h; Display Combination CodeA-11                                             | AH=1Ah;.  | A.22  |

| h;Return VGA Functionality and State InformationA-12                        | AH=1Bh;   | A.23  |

| h; Save and Restore Video StateA-15                                         | AH=1Ch;   | A.24  |

|                                                                             |           |       |

### Appendix B: Extended BIOS Function Calls

| <b>B</b> .1 | Scope  |                                                                              |

|-------------|--------|------------------------------------------------------------------------------|

| B.2         | BIOS E | ExtensionsB-2                                                                |

|             | B.2.1  | Video BIOS Base Address                                                      |

|             | B.2.2  | Calling Extended Functions                                                   |

|             | B.2.3  | Compatibility                                                                |

|             | B.2.4  | Extended BIOS Services                                                       |

|             | B.2.5  | Function 00h - Set Display Mode                                              |

|             | B.2.6  | Function 01h - Set Display Controller State                                  |

|             | B.2.7  | Function 02h - Set DAC State                                                 |

|             | B.2.8  | Function 03h - Program Specified Clock Entry                                 |

|             | B.2.9  | Function 04h - Short Query Function 0                                        |

|             | B.2.10 | Function 05h - Short Query Function 1                                        |

|             | B.2.11 | Function 06h - Short Query Function 2                                        |

|             |        | Function 07h - Query Graphics Hardware Capability and Capture Width Info B-7 |

|             |        | Function 08h - Query Installed Modes                                         |

|             | B.2.14 | Function 09h - Query Supported Mode                                          |

|             | B.2.15 | Function 0Ah - Display Power Management Service (DPMS)                       |

|             | B.2.16 | Function 0Bh - Display Data Channel (DDC) Service                            |

|             | B.2.17 | Function 0Ch - Save and Restore Graphics Controller Data                     |

|             |        |                                                                              |

|     | B.2.18 | Function 0Dh - Get/Set Refresh Rate (CRT only) | . <i>B-12</i> |

|-----|--------|------------------------------------------------|---------------|

|     | B.2.19 | Function 14h - Detect CRT/TV/DFP               | . <b>B-13</b> |

|     | B.2.20 | Function 15h - Get/Set Active Display(s)       | . <i>B-14</i> |

|     |        | Function 16h - Get/Set TV Standard.            |               |

|     | B.2.22 | Function 17h - Get TVOut Info                  | . <b>B-15</b> |

| B.3 | Mode 7 | Fable Structure                                | <i>B-16</i>   |

|     | B.3.1  | CRTC Parameter Table                           | .B-16         |

| B.4 | RAGE   | 128 Internal Parameter Table Format            | .B-17         |

|     |        | CRTC Parameter Table                           |               |

|     |        |                                                |               |

### Appendix C: BIOS Header, Scratch Registers and Information Tables

| C.1 | Scope.  |                 | <i>C-1</i> |

|-----|---------|-----------------|------------|

| C.2 | Video I | BIOS Header     | <i>C-2</i> |

| C.3 | Scratch | Registers       | <i>C-6</i> |

| C.4 | Informa | ation Tables    | <i>C-8</i> |

|     | C.4.1   | TV Information  | <i>C-8</i> |

|     |         | DFP Information |            |

### Appendix D: VESA BIOS Extension

| D.1 Scope                                            | <i>D-1</i>  |

|------------------------------------------------------|-------------|

| D.2 Status Information                               | <i>D-2</i>  |

| D.3 Function 00h - Return Super VGA Information      | <i>D-3</i>  |

| D.4 Function 01h - Return Super VGA Mode Information | <i>D-6</i>  |

| D.5 Function 02h - Set Super VGA Video Mode          | <i>D-12</i> |

| D.6 Function 03h - Return Current Video Mode         | <i>D-13</i> |

| D.7 Function 04h - Save/Restore State                | <i>D-14</i> |

| D.8 Function 05h - Display Window Control            | <i>D-15</i> |

| D.9 Function 06h - Set/Get Logical Scan Line Length  | <i>D-17</i> |

| D.10 Function 07h - Set/Get Display Start            | <i>D-18</i> |

| D.11 Function 08h - Set/Get AC Palette Format        | <i>D-19</i> |

| D.11.1 Subfunction 0 - Set AC Palette Format         | <i>D-19</i> |

| D.11.2 Subfunction 1 - Get AC Palette Format         | <i>D-19</i> |

| D.12 Function 09h - Set/Get AC Palette Data          | <i>D-20</i> |

| D.13 Power Management Services.                      | <i>D-21</i> |

| D-21        |

|-------------|

| <i>D-21</i> |

| <i>D-21</i> |

| D-23        |

| <i>D-23</i> |

| <i>D-24</i> |

|             |

### Appendix E: BIOS Hardware Configuration and Multimedia Tables

| E.1 | Scope |                                           | <i>E-1</i>  |

|-----|-------|-------------------------------------------|-------------|

| E.2 | BIOS  | Multimedia Table                          | <i>E-2</i>  |

| E.3 | BIOS  | Hardware Configuration Table              | <i>E</i> -8 |

| E.4 | BIOS  | Tables for RAGE 128 / RAGE THEATER Board. | <i>E-10</i> |

|     | E.4.1 | Multimedia Table                          | <i>E-10</i> |

|     |       | Hardware Configuration Table              |             |

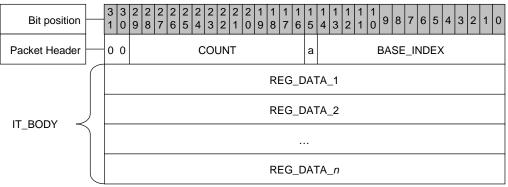

### Appendix F: CCE Command Packets

| F.1 Scope                      | <i>F-1</i>  |

|--------------------------------|-------------|

| F.2 Notation used this Section | <i>F-2</i>  |

| 7.13 Type-0 CCE Packet         |             |

| F.3 Type 1 CCE Packet          | <i>F</i> -5 |

| F.4 Type 2 CCE Packet          | <i>F</i> -7 |

| F.5 Type 3 CCE Packet          | <i>F</i> -8 |

| F.6 Summary of the CEE Packets | <i>F-10</i> |

| F.7 2D Packets                 |             |

| F.8 NOP                        | <i>F-19</i> |

| F.9 PAINT                      |             |

| F.10 SMALL_TEXT.               |             |

| F.11 HOSTDATA_BLT              |             |

| F.12 POLYLINE                  |             |

| F.13 SCALE                     |             |

| F.14 TRANS_SCALE               |             |

| F.15 POLYSCANLINES             | <i>F-39</i> |

| F.16 NEXTCHAR                  |             |

| F.17 PAINT_MULTIF-41            |

|---------------------------------|

| F.18 BITBLT_MULTIF-42           |

| F.19 TRANS_BITBLT               |

| F.19.1 CLR_CMP_CNTLF-43         |

| F.20 PLY_NEXTSCANF-45           |

| F.21 LOAD_PALETTE               |

| F.22 SET_SCISSORS               |

| F.23 SET_MODE_24BPP             |

| F.24 3D_RNDR_GEN_PRIM           |

| F.24.1 VC_FORMAT                |

| F.24.2 VC_CNTL                  |

| F.24.3 FTLVERTEX                |

| F.25 Interpretation of Vertices |

| F.25.1 Points (1)               |

| F.25.2 Lines (2)                |

| F.25.3 Polylines (3)            |

| F.25.4 Triangles (4)            |

| F.25.5 Triangle Fan (5)         |

| F.25.6 Triangle Strip (6)       |

| F.26 3D_RNDR_GEN_INDX_PRIM      |

| F.26.1 Vertex Array Format      |

| F.27 NEXT_VERTEX_BUNDLE         |

### Appendix G: List of Tables

### Appendix H: List of Figures

### Appendix I: List of Example Code

### Appendix J: Revision History

| J.1 | SDK-G04000 | Rev 0.01 (SD40001.pdf) | H-3 | 1 |

|-----|------------|------------------------|-----|---|

|-----|------------|------------------------|-----|---|

## 1.1 Scope

This manual is a programming guide for the RAGE 128 graphics controller. The examples that are provided show how to program typical 2D and 3D drawing operations. This manual also provides details about various multimedia concepts.

For details about programming older generations of ATI graphics controller, refer to the *mach64 Programmer's Guide*. To request this manual, contact the ATI Developer Relations Department.

### Background

The RAGE 128 is a fully integrated 128-bit graphics and multimedia accelerator. It combines astoundingly fast 3D and 2D acceleration with advanced multimedia capabilities. This accelerator incorporates new technologies such as Concurrent Command Execution (CCE). CCE was previously known as Programming Model 4 (PM4). CCE uses the RAGE 128's bus mastering capabilities to deliver excellent drawing performance, as well as simplifying the programming effort.

# 1.2 Major Features of the RAGE 128

- Highly optimized 128-bit engine.

- Triple 8-bit palette DAC with gamma correction for true WYSIWYG color. Pixel rates up to 250MHz (optional); 230MHz standard.

- Supports a variety of memory configurations for bandwidths of up to 2GB/s.

- Single Data Rate (SDR) SGRAM or SDRAM at up to 125MHz on a 128-bit interface (2GB/s).

- Double Data Rate (DDR) SGRAM at up to 125 MHz on a 64-bit interface (2GB/s).

- SDR SGRAM or SDRAM at up to 143MHz on a 64-bit interface (1.1GB/s)

- Flexible graphics memory configurations:

- 2MB up to 32MB SDRAM or SDR/DDR SGRAM.

- DDC1 and DDC2B+ for plug and play monitors.

- Single-chip solution in 0.25µm, 2.5V CMOS technology.

- Package options available for specific features.

- Hardware acceleration for the following:

- BitBlt

- Line Draw

- Polygon/Rectangle Fill

- Bit Masking

- Monochrome Expansion

- Panning/Scrolling

- Scissoring

- Full ROP support and hardware cursor (up to 64x64x2)

- Game acceleration including support for Microsoft's DirectDraw, Double Buffering, Virtual Sprites, Transparent Blit, and Masked Blit.

- Acceleration in 8-, 16-, 24-, 32-bpp modes.

# **1.3** A Chapter Summary of this Manual

#### Table 1-1 Chapter Summary

| Chapter                                                          | Description                                                                                                                                                        |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>Overview                                                    | Scope of the manual.<br>Overview of the contents.<br>Feature summary of the RAGE 128.                                                                              |

| 2<br>Using the RAGE 128                                          | Basic programming guide.<br>A general understanding of the features and functions.                                                                                 |

| 3<br>Getting Started                                             | Using the RAGE 128 in accelerator mode:<br>Card detection, setting a display mode, engine initialization,<br>programming considerations.                           |

| 4<br>Programmed I/O<br>Operations                                | Issues covering the accelerator engine:<br>Command FIFO queue<br>Programmed I/O operations (such as bit block transfers, line,<br>pattern, and rectangle drawing). |

| 5<br>Concurrent Command<br>Execution Initialization<br>and Usage | Overview of the CCE programming model:<br>Setup and initialization of the CCE in various operational modes.                                                        |

| 6<br>CCE Packets                                                 | Description of the CCE packets.<br>Programming examples for general engine operations (blts,<br>rectangle and line draws, etc.).                                   |

| 7<br>Advanced Topics                                             | Advanced topics covering special features and capabilities:<br>Using the overlay scalar and front-end scalar.<br>Using the bus mastering features.                 |

| Appendix A                                                       | BIOS Function Calls                                                                                                                                                |

| Appendix B                                                       | Extended BIOS Function Calls                                                                                                                                       |

| Appendix C                                                       | BIOS Header, Scratch Registers and Information Tables                                                                                                              |

| Appendix D                                                       | VESA BIOS Extension                                                                                                                                                |

| Appendix E                                                       | BIOS Hardware Configuration and Multimedia Tables                                                                                                                  |

| Appendix F                                                       | CEE Command Packets                                                                                                                                                |

# 1.4 Notations and Conventions Used in this Manual

A mnemonic is used to identify the name of a hardware register. The naming conventions for registers and/or bit fields within a register are as follows:

- Register\_Mnemonic

- Register\_Mnemonic[Bit\_Numbers]

- Field\_Name@Register\_Mnemonic

The following example is the mnemonic for the Configuration Chip ID register:

• CONFIG\_CHIP\_ID

Continuing the above example, the Product Type Code field within the above register occupies bit positions [0] through [15]. The examples below describe this field in two ways:

- CONFIG\_CHIP\_ID[15:0]

- CFG\_CHIP\_TYPE@CONFIG\_CHIP\_ID

The second convention will be the preferred one, with the first convention used mostly for describing unnamed fields.

Hexadecimal numbers will either be prefixed with "0x" (C-style) or appended with "h" (Intel assembly-style). Binary numbers will be appended with "b". All other numbers are in decimal.

Sample code and functions will be typeset in a courier font.

#### Example: performing an operation

```

// Sample Function

void Sample_function (void)

{

printf ("This is a sample function\n");

} // Sample_function

```

# **1.5** Nomenclature and Conventions

These conventions apply to the RAGE 128 Register Reference Manual.

### 1.5.1 Register and Field Names

An upper-case mnemonic represents the name of a hardware register and field names. The naming conventions for registers and bit fields are as indicated below:

### **REGISTER\_MNEMONIC**

$Example: {\tt CONFIG\_CHIP\_ID} \ is the mnemonic for the Configuration Chip ID register.$

#### REGISTER\_MNEMONIC[Bit\_Numbers] - OR-FIELD NAME@REGISTER MNEMONIC

For example, **CONFIG\_CHIP\_ID[15:0]** refers to the bit field that occupies bit positions [0] through [15] within this register.

**CFG\_CHIP\_TYPE@CONFIG\_CHIP\_ID** gives the field name **CFG\_CHIP\_TYPE** (Product Type Code) instead of the bits position.

### 1.5.2 Numeric Representations

- Hexadecimal numbers are appended with "h" whenever there is a risk of ambiguity. Other numbers are assumed to be in decimal.

- Registers (or fields) of identical function are sometimes indicated by a single expression in which the part of the signal name that differs is enclosed in [] brackets. For example, the eight Host Data registers HOST\_DATA0 through to HOST\_DATA7 are represented by the single expression HOST\_DATA[7:0].

### **1.5.3 Register Description**

All registers in this document are described with the format of the self-explained sample table below. All offsets are in hexadecimal notation, while programmed bits are in either binomial or hexadecimal notation. (Note: sometimes not shown are the indirect type of byte offsets, e.g., CFG, PLL, VGA, etc., which will be indicated on the appropriate registers).

This page intentionally left blank.

# **Chapter 2 Programming Basics**

# 2.1 Scope

This chapter details the basics about the RAGE 128's operation and drawing modes. The following topics are covered:

- Functional block diagram of the RAGE 128.

- Operation modes.

- Accelerator programming modes.

- Review of imaging terminology.

- Display modes and switching modes.

# 2.2 Overview

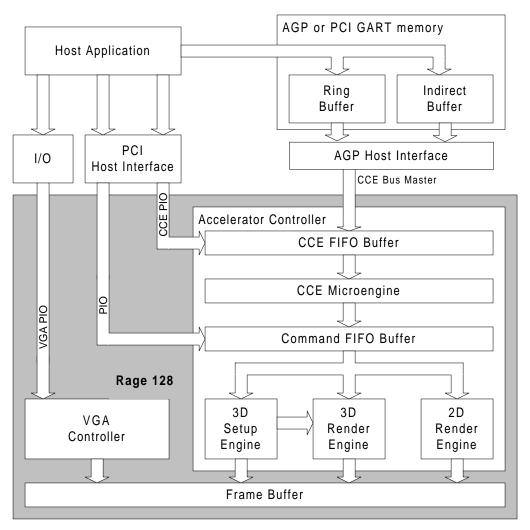

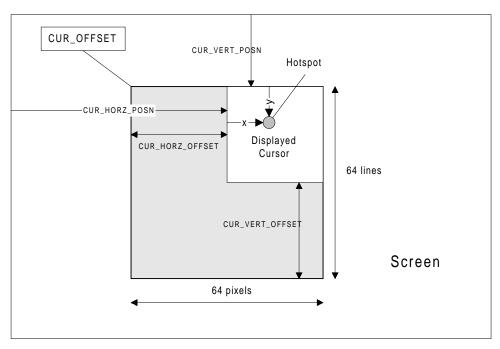

Figure 2-1. RAGE 128 Structure and Data Flow

This chapter presents a basic description of the functional blocks in this diagram. Detailed descriptions are presented in subsequent chapters. For a summary of the RAGE 128's functional blocks, *refer to Table 2-1*. For a summary of the RAGE 128's buffers, *refer to Table 2-2*.

| Functional Unit                              | Purpose                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Accelerated Graphics<br>Port (AGP) Interface | Transfers data from the ring buffer (located in the system memory) to the RAGE 128's CCE FIFO buffer without direct involvement of the CPU. |

| VGA Controller                               | Manages pixel operations under VGA mode.                                                                                                    |

| CCE Microengine                              | Parses the command packets from the host application and places the results into the Command FIFO buffer.                                   |

| 2D Render Engine                             | Performs 2D primitive rasterization.                                                                                                        |

| 3D Render Engine                             | Performs 3D primitive rasterization.                                                                                                        |

| 3D Setup Engine                              | Performs 3D primitive setup operations.                                                                                                     |

#### Table 2-1 RAGE 128 Functional Blocks

#### Table 2-2 RAGE 128 Buffers

| Buffer Name            | Size                                                                                  | Purpose                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CCE FIFO<br>Buffer     | 192 DWORDs                                                                            | Contains command packet data queued for processing<br>by the micro controller. Only used in CCE-programming<br>mode.                                                                                                                |

| Command FIFO<br>Buffer | 192 DWORDs                                                                            | Contains register/data pairs for processing by the 3D-setup, 3D-render, and 2D-render engines (i.e., GUI engine). Data is written directly in PIO-programming mode, and streamed from the micro controller in CCE-programming mode. |

| Frame Buffer           | Depends on the<br>amount of video<br>memory installed.<br>Ranges from 8MB<br>to 32MB. | Contains all on-screen and off-screen rendering<br>buffers, such as: drawing, stencil and z buffers,<br>bitmaps, and texture maps.                                                                                                  |

# 2.3 Operation Modes

The RAGE 128 operates in two distinct modes:

- VGA mode.

- Accelerator mode.

These modes are mutually exclusive. However, they share the same frame-buffer memory and I/O ports. They are described in the following sections.

### 2.3.1 VGA Mode

VGA (Video Graphics Adapter) is an established industry standard created by IBM. When operating in VGA mode, the host application draws directly into the frame buffer using the VGA controller. The accelerator controller is disabled and no rendering operations are accelerated. The VGA controller and the data path from the host application to the frame buffer are shown in the figure (*refer to Figure 2-1.*). The VGA Controller registers are programmed using conventional I/O.

There are many published texts that describe VGA programming. Consequently, this manual does not cover programming the VGA controller. For a comprehensive, informative source on this subject, refer to *Programmer's Guide to the EGA*, *VGA*, *and Super VGA Cards* by Richard F. Ferraro.

For Super VGA programming, the RAGE 128 supports the Video Electronics Standard Association (VESA) Video BIOS Extension (VBE) 2.0 programming interface. This interface was created by VESA to provide a standard, hardware independent method for using Super VGA display modes. Contact VESA for more information about VBE.

### 2.3.2 Accelerator Mode

When operating in accelerator mode, rendering operations are performed by the RAGE 128's accelerator controller. The VGA controller is disabled. The host application is limited to setting up the accelerator controller, and the controller renders directly to the frame buffer.

The accelerator controller contains the following three engines:

- 2D Rendering Engine that performs 2D rasterization.

- 3D Setup engine that performs 3D primitive setup operations.

• 3D Render Engine that performs 3D rasterization.

The three engines are collectively referred to as the Graphical User Interface (GUI) engine (*refer to Figure 2-1*.).

The following two modes are used to program the GUI engine:

- Programmable Input and Output (PIO) mode.

- Concurrent Command Execution (CCE) mode.

These programming modes are described in the following sections.

# 2.4 Drawing Modes in Acceleration-operation Mode

### Programmable I/O (PIO) Mode

In this mode, the host application programs the GUI engine by writing directly to the RAGE 128's memory-mapped registers. The registers are written through one of the RAGE 128's two register apertures over the bus interface. The register writes are queued in the RAGE 128's internal 192 entry Command FIFO buffer as register-datum pairs. These Command FIFO buffer entries are processed by the GUI engine to draw into the frame buffer.

To see the data path from the host application to the Command FIFO, refer to Figure 2-1.

For more details about the PIO-mode programming, refer to Chapter 4.

For more details about the RAGE 128's register apertures, refer to 2.6.

### **Concurrent Command Execution (CCE) Programming Mode**

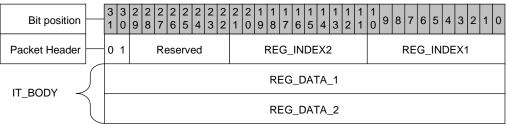

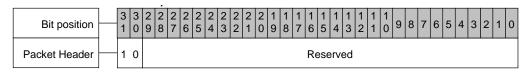

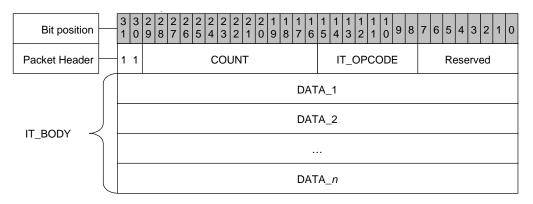

In this mode, the host sends commands to the RAGE 128 in the form of *command packets*. A command packet is a data block that consists of a header followed by a variable size data body. Within the RAGE 128, the packets are queued in the 192 entry CCE FIFO buffer. A micro controller processes the packets, produces the conventional register data, and feeds this data to the Command FIFO buffer. The Command FIFO buffer data is processed (as it is in PIO mode) to render into the frame buffer.

The host application transfers packets to the CCE FIFO buffer using the following two methods:

- Write them directly into the CCE FIFO buffer through memory-mapped register writes over the bus interface.

- Queue them in system memory buffers and bus-master them to the CCE FIFO buffer.

The second method is by far the most efficient for programming the RAGE 128. ATI highly recommends using the bus-mastered CCE programming mode as the primary programming method. Streaming packets in this manner enables significant concurrency between the host and the RAGE 128. In addition, there are several predefined single-purpose packets that greatly simplify the programming of common drawing operations.

The RAGE 128 uses the following two mechanisms for bus-mastering packets to the CCE FIFO buffer:

- Ring buffer

- Indirect buffer

These mechanisms are described in the following sections.

### **Ring Buffer**

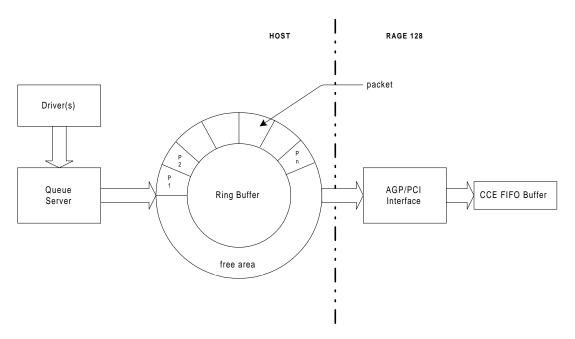

The ring buffer is a continuous block of memory allocated by the host application in AGP or PCI GART memory. The PCI GART is a mechanism for simulating AGP functionality on the RAGE 128 over the PCI bus. For more details about the PCI GART, *refer to 2.6.6.* The host and RAGE 128 treat this buffer as a circular buffer by wrapping back to the starting address when they reach the end. The starting address and the size of the buffer are passed to the RAGE 128 when initializing the CCE bus-mastering mode.

The application copies packets into the ring buffer in consecutive order starting at the top. It instructs the RAGE 128 where to read the next packet by writing to a CCE write-pointer register. The RAGE 128 triggers bus-mastering operations to transfer packets from the ring buffer to its CCE FIFO buffer according to watermarks set during CCE initialization. After completing the transfer, the RAGE 128 uses bus-mastering to update a host application read-pointer to indicate where it has read to in the ring buffer. The physical address of this pointer is passed to the RAGE 128 during CCE initialization.

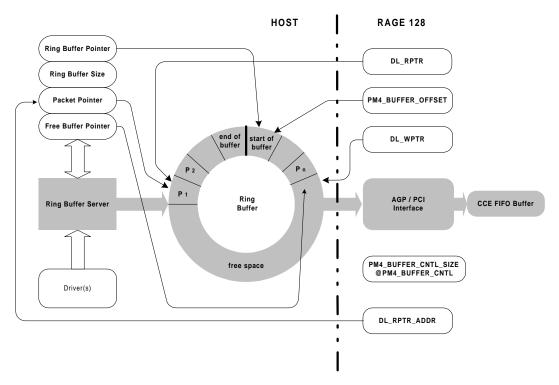

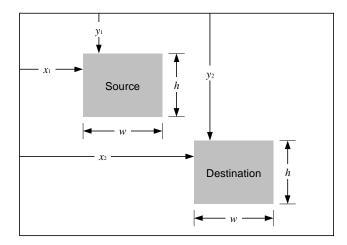

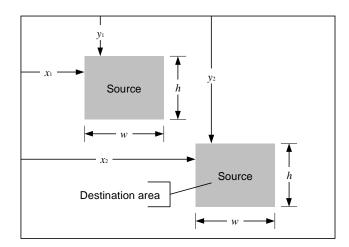

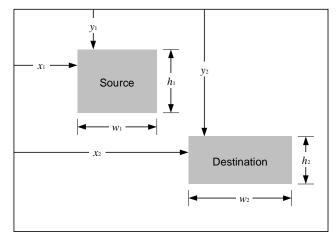

To view a diagram of the ring buffer, *refer to Figure 2-2*.

For more details about programming the ring buffer refer to Chapter 5.

Figure 2-2. The Ring Buffer

### **Ring Buffer Queue Server**

For multitasking operating systems where multiple clients may require synchronized access to the graphics resources, it may be beneficial to employ a queue server mechanism to arbitrate and control access to the ring buffer. This mechanism could enumerate clients and use semaphores to synchronize and protect access.

For an example of how to submit packets using such a mechanism, refer to Chapter 5.

### **Indirect Buffer**

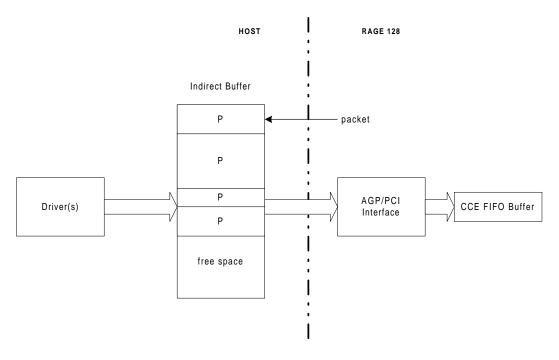

The indirect buffer is a contiguous block of memory allocated by the host application in AGP or PCI GART memory. The host and RAGE 128 treat this as a linear buffer. They do not employ any buffer wrapping mechanisms for the indirect buffer.

The indirect buffer is similar to the ring buffer in that the host places packets in it and the RAGE 128 transfers them out using bus-mastering. But while the ring buffer is meant to be continuously updated, which results in content being constantly overwritten, the

indirect buffer may be filled with static packets that are merely updated but not completely overwritten. This is a more efficient way to handle common or frequently used packets such as blits, rectangle fills, etc. One additional difference is that packets may be placed and accessed from the indirect buffer in arbitrary order.

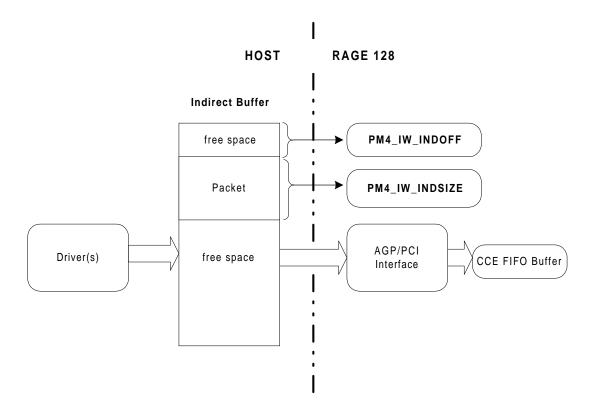

A packet transfer is initiated by writing the offset from the start of the indirect buffer and the size of the packet to specific registers. For more details about this procedure, *refer to* 5.3.

The most efficient combination is to use both the ring buffer and the indirect buffer. The indirect buffer may be used for storing frequently used packets, and the ring buffer may be used for general command streaming. Packets can be used to write to specific registers, so the register writes that trigger indirect buffer transfers can also be streamed as ring buffer packets. If the ring buffer is not used, these registers may be written through PIO.

To view a conceptual diagram of the indirect buffer, refer to Figure 2-3.

Figure 2-3. The Indirect Buffer

# 2.5 Review of Imaging Terminology

This section describes some background and terms about computer imaging.

### 2.5.1 Raster Image

Due to CRT (*Cathode Ray Tube*) technology, an image is broken into a number of equally spaced *scanlines*. Each scanline may be further broken into a number of smallest-viewable elements, called *pixels*. This type of image is commonly referred to as *raster image*.

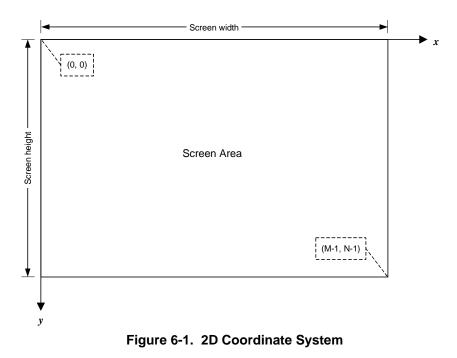

The process of breaking an ordinary image into a raster image is called *rasterization*. This process allows an *M*-by-*N* array to represent an image, where:

- *M* represents the width of the image.

- *N* represents the height of the image (with its x-coordinate pointing to the right and y-coordinate pointing downwards).

The value of an element in this array represents the pixel's *color intensity*. This setup allows the video memory to contain the features of an image (i.e. image dimensions and color depth).

The *screen image* is the case where the raster image covers the entire CRT screen. The origin of the coordinate system is at top-left corner of the screen, where:

- The width of the image equals the number of pixels per scanline of the screen.

- The height is the number of scanlines that the screen has.

# 2.5.2 True RGB Color

Color in the real world is called *natural color* and it is represented as an analog quantity. Color from a CRT screen is called *digitized color* and it is represented as a digital quantity. The digitized-color value is an approximate of the natural-color value. The analog value can represent by an infinite number of color values. However, the digital value is limited in the number of unique (i.e. distinctive) colors.

For example, the maximum number of distinctive colors currently defined for this approximation is about 16 million (i.e.  $2^{24}$ ).

Each digitized color is represented by a combination of three *color components* (*Red*, *Green*, and *Blue*). The intensity of each component is divided into 256 levels. Zero intensity represents the lowest value and '255' represents the highest. Each component needs 8 bits. Therefore, to represent a color made up of a R, G, and B component, 24 bits are needed. This representation of digitized color is referred to as the *True RGB color*.

### 2.5.3 Representing Pixels

A RAGE 128 can display monochrome and color images.

- Monochrome images refer to text.

- Color images refer to digitized color photographs, movies, and computer-generated color images.

### **Monochrome Images**

Monochrome images are composed of pixels that can have just one of two digitized colors (i.e. black and white). Each pixel's color is represented by one bit (i.e. '0' for black and '1' for white).

The depth of the pixel is one *bit per pixel* (bpp). Monochrome pixels may be assigned with any two digitized colors, one representing the *foreground color*, such as *white*, and the other representing the *background color*, such as *black*.

To display blue-colored text on a background of white, a '0' represents the color *blue* and a '1' represents the color *white*. This type of treatment to monochrome images is termed *color expansion*. In fact, the realization of pixels in a mono image is done by mapping 0's and 1's onto background and foreground colors represented in the RGB format, although the memory representation of the pixels is one bpp.

### Formats for Various Color Images

Color images may be represented in 8-, 15-, 16-, 24-, and 32-bpps formats (i.e.  $2^8$ ,  $2^{15}$ ,  $2^{16}$ ,  $2^{24}$  colors respectively).

The number of colors that can be displayed in the 32-bpp format is  $2^{24}$  because the most significant eight bits of the 32 bits are not used. Using the byte as a measure of memory:

- One byte to represent a pixel for the 8-bpp format.

- Two bytes for the 15- and 16-bpp formats.

- Three bytes for the 24-bpp format.

- Four bytes for the 32-bpp format.

#### 1-bpp Format

#### Table 2-3 1-bpp Format (left-to-right)

| 1-bpp, BYTE_PIX_ORDER = 0 (left-to-right), Draw Engine Only |                         |                         |                                |  |

|-------------------------------------------------------------|-------------------------|-------------------------|--------------------------------|--|

| Structure of the Drawing Data as Used by the RAGE 128       |                         |                         |                                |  |

| 19 1A 1B 1C 1D 1E 1F 20                                     | 11 12 13 14 15 16 17 18 | 9 A B C D E F 10        | 1 2 3 4 5 6 7 8                |  |

| Drawing Data Placed in Video Memory                         |                         |                         |                                |  |

| 1 2 3 4 5 6 7 8<br>LSB                                      | 9 A B C D E F 10        | 11 12 13 14 15 16 17 18 | 19 1A 1B 1C 1D 1E 1F 20<br>MSB |  |

#### Table 2-4 1-bpp Format (right-to-left)

| 1-bpp Format, BYTE_PIX_ORDER = 1 (right-to-left), Draw Engine Only |                         |                         |                         |  |  |

|--------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|--|--|

| Structure of the Drawing Data as Used by the RAGE 128              |                         |                         |                         |  |  |

| 20 1F 1E 1D 1C 1B 1A 19                                            | 18 17 16 15 14 13 12 11 | 10 F E D C B A 9        | 8 7 6 5 4 3 2 1         |  |  |

| Drawing Data Placed in Video Memory                                |                         |                         |                         |  |  |

| 8 7 6 5 4 3 2 1                                                    | 10 F E D C B A 9        | 18 17 16 15 14 13 12 11 | 20 1F 1E 1D 1C 1B 1A 19 |  |  |

### 8-bpp Format

The value of a pixel does not represent the intensity of a color. Instead, it represents the index of the color table, called the *color palette*. The palette stores all of the possible colors that could be used. The host application uses this value to point to a specific color in the palette. Color represented in the 8-bpp format is known as *pseudo-color*.

#### Table 2-5 8-bpp Pseudo-color Format

| 8-bpp Pseudo-color Format |                             |                           |            |  |

|---------------------------|-----------------------------|---------------------------|------------|--|

|                           | Structure of the Drawing Da | a as Used by the RAGE 128 |            |  |

| 4<br>(MSB)                | 3                           | 2                         | 1<br>(LSB) |  |

|                           | Drawing Data Place          | ed in Video Memory        |            |  |

| 1<br>(LSB)                | 2                           | 3                         | 4<br>(MSB) |  |

### 15-bpp, aRGB, or 1555 Format

This format uses two bytes to represent the three color components (Red, Green, and Blue). Each component uses five bits to represent its intensity.

- Bit [15] is not used (shown in the table as 'a').

- Bits [14:10] represent red.

- Bits [9:5] represent green.

- Bits [4:0] represent blue.

#### Table 2-6 15-bpp, aRGB, or 1555 Format

|                  | Structure of the Drawing Dat | a as Used by the RAGE 128 |               |

|------------------|------------------------------|---------------------------|---------------|

| Pixe<br>aRRRRRGG | Pixe<br>aRRRRRGG             | el #1<br>GGGBBBBBB        |               |

|                  | Drawing Data Place           | ed in Video Memory        |               |

| Pixel #1 low     | Pixel #1 high                | Pixel #2 low              | Pixel #2 high |

| GGGBBBBB         | aRRRRRGG                     | GGGBBBBB                  | aRRRRRGG      |

Sometimes this dummy bit maybe used for 3D rendering. For typical applications, this bit not used.

#### 16-bpp, RGB, or 565 format

This format is similar to the 15-bpp format:

- Bits [15:10] represent red

- Bits [10:5] represent green

- Bits [4:0] represent blue.

#### Table 2-7 16-bpp, RGB, 565 Format

| 16-bpp, RGB, 565 Format                               |                           |                             |                           |  |  |

|-------------------------------------------------------|---------------------------|-----------------------------|---------------------------|--|--|

| Structure of the Drawing Data as Used by the RAGE 128 |                           |                             |                           |  |  |

| Pixel #2<br>RRRRRGGGGGBBBBB                           |                           | Pixel #1<br>RRRRRGGGGGBBBBB |                           |  |  |

| Drawing Data Placed in Video Memory                   |                           |                             |                           |  |  |

| Pixel #1 low<br>GGGBBBBB                              | Pixel #1 high<br>RRRRRGGG | Pixel #2 low<br>GGGBBBBB    | Pixel #2 high<br>RRRRRGGG |  |  |

### 24-bpp Format

Each color component uses a byte to represent its intensity.

|    | Structure of the Drawing Dat | a as Used by the RAGE 128 |    |

|----|------------------------------|---------------------------|----|

| B2 | R1                           | G1                        | B1 |

| G3 | B3                           | R2                        | G2 |

| R4 | G4                           | B4                        | R3 |

|    | Drawing Data Place           | ed in Video Memory        |    |

| B1 | G1                           | R1                        | B2 |

| G2 | R2                           | B3                        | G3 |

| R3 | B4                           | G4                        | R4 |

### Table 2-8 24-bpp Format (display only)

#### 32-bpp, RGBa, or 8888 Format

This format is similar to the 24-bpp format with the addition of a dummy byte.

#### Table 2-9 32-bpp, RGBa, or 8888 Format

| 32-bpp, RGBa, or 8888 Format                          |   |   |   |  |  |

|-------------------------------------------------------|---|---|---|--|--|

| Structure of the Drawing Data as Used by the RAGE 128 |   |   |   |  |  |

| а                                                     | R | G | В |  |  |

| Drawing Data Placed in Video Memory                   |   |   |   |  |  |

| В                                                     | G | R | а |  |  |

### 2.5.4 Pixels

The RAGE 128 supports pixel depths of 1, 8, 15, 16, and 32 bits per pixel. When operated in the 24-bpp format mode, some software assistance is required.

The pixels are consumed from the most significant bit (MSB) to the least significant bit (LSB) (or vise versa, depending on the rage 128's configuration).

The following shows the bit definitions of the pixel formats in BYTE and DWORD representations (i.e., this is the 'little endian' representation):

- The ordinal values represent the ordering of the pixels in memory for a left to right pixel trajectory beginning on a DWORD boundary.

- The ordinal value '1' represents the position in memory of the left-most pixel in the

DWORD.

• The color components are denoted as R, G, and B.

## 2.5.5 Pitch

In ATI terminology, *pitch* measures the size of memory for representing a scanline of pixels. Due to the RAGE 128's design, this measure must satisfy the following two requirements:

- Pitch must be an integer multiple of eight pixels. If the number of pixels per scanline does not meet this requirement, add the required number of dummy pixels to the scanline.

- The memory size of a pitch must be a multiple of 16 bytes.

If we denote the number of pixels per scanline by m, the number of added dummy pixels by n, and the number of bytes used to representing a pixel by l, the two requirements can be written as:

$$(m+n)$$

MOD 8 = 0 Equation 2.1

$$l \times (m+n) \operatorname{MOD} 16 = 0$$

Equation 2.2

Since l is restricted to values 1/8 for monochrome images, and 1, 2, 3, and 4 for color images, it is easy to show that Equation 2.1 is implied by Equation 2.2.

Using Equation 2.2, the number of dummy pixels can be calculated by the following equation:

$$n = \begin{cases} 128 - m \text{ MOD } 128 & l = 1/8 \\ 16 - m \text{ MOD } 16 & l = 1, 3 \\ 8 - m \text{ MOD } 8 & l = 2 \\ 4 - m \text{ MOD } 4 & l = 4 \end{cases}$$

Equation 2.3

Using Equation 2.3, the pitch can be written as:

$$Pitch = \frac{m+n}{8}$$

Equation 2.4

The size of memory for the pitch is:

$$PitchMemSize = l \times Pitch \times 8$$

Equation 2.5

Equation 2.3, Equation 2.4, and Equation 2.5 are also applicable to the pitch of the bitmap, where *m* corresponds to the width of the bitmap. According to these equations, the pitch of an 800x600 screen can be 100 units of eight pixels, and the corresponding memory size is 1600 bytes ( $2 \ge 100 \ge 8$ ) provided each pixel is represented by 16-bit color. To enable the block-write capability of the RAGE 128, the second requirement on defining a pitch must be changed to 128-byte alignment. This leads to a modification of Equation 2.2, which can be rewritten as:

$$l \times (m+n) \text{ MOD } 128 = 0$$

Equation 2.6

In addition, a corresponding modification to the calculation of dummy pixels has to be made; this effort is left for you.

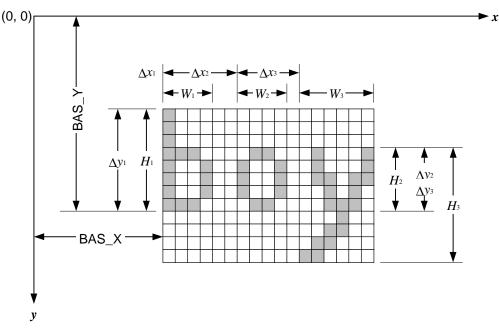

### 2.5.6 Video Memory

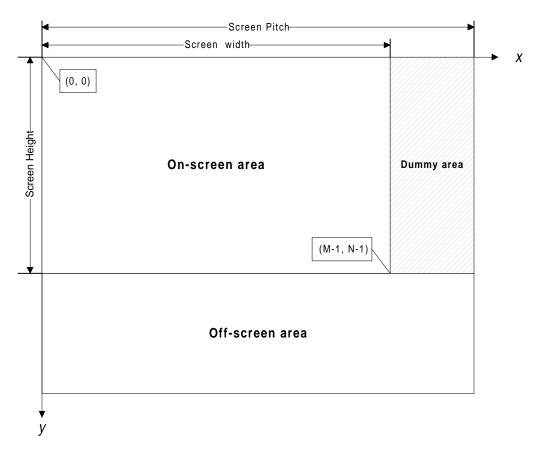

The RAGE 128 uses the *video memory* (i.e. the *frame buffer*) to display geometrical images on the CRT's screen. The frame buffer is further divided into the following areas:

- The *on-screen area* represents the entire screen image.

- The *dummy area* makes up the pitch of screen due to the hardware requirement.

- The *off-screen area* stores information about the image (e.g. bitmaps). There are some conditions when there is no off-screen area (e.g. the video memory may contain the on-screen data and any unused areas contain data about the depth of the pixels).

As a result of the equations developed in the previous section, it is easy to calculate the allocation of the video memory when a display configuration is given.

For example, the required display configuration is 800x600 pixels in the 16-bpp format mode. Then, the calculated memory size for the on-screen area is 960,000 bytes.

Therefore, the minimum size for the video memory must be 1MB. If the size of the video memory is 4MB, there will be more than 3MB left over for the off-screen area. The RAGE 128 can support up to a maximum of 32MB of video memory.

### Video Memory Addressing

Conventionally, the lowest address of the video memory corresponds to the top-left corner of the on-screen area, and the highest address to the bottom-right corner of the off-screen area.

For example, the video memory is 4MB. Then, the following conditions are true:

- The top-left corner of screen corresponds to address 0.

- The bottom-right corner of the off-screen area corresponds to 0xFFFFF.

The RAGE 128 addresses the video memory from zero to the upper bound. The video memory address seen by RAGE 128 is called the *Physical Memory Address*.

To begin drawing to the top-left corner of the CRT screen, set registers **SRC\_OFFSET** and **DST\_OFFSET** to zero. These two registers can be set to any value within the address space of video memory.

Figure 2-4. Video Memory

# 2.6 Memory Apertures

The RAGE 128 requires memory apertures from the system. These apertures map the video memory and registers onto the host's memory space. By using this mapping, the host application can access the frame buffer and the memory-mapped registers as if they were part of the system memory.

The following are the types of apertures that exist within the system space:

- The *register aperture* is used for the memory-mapped registers that are related to the RAGE 128.

- The video aperture.

Normally, the apertures are located somewhere within the 4GB address space where it does not conflict with the system (host) memory. Further, an aperture must be located on a 32MB boundary.

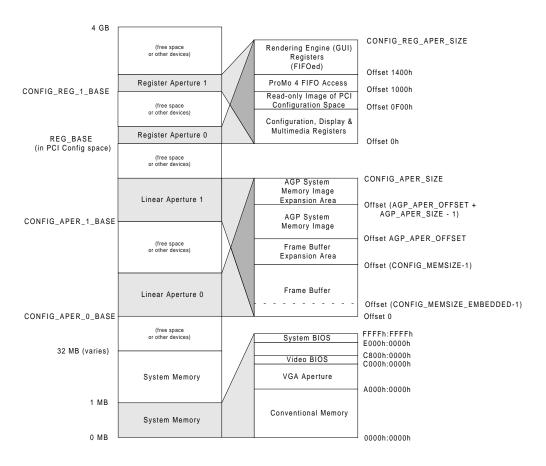

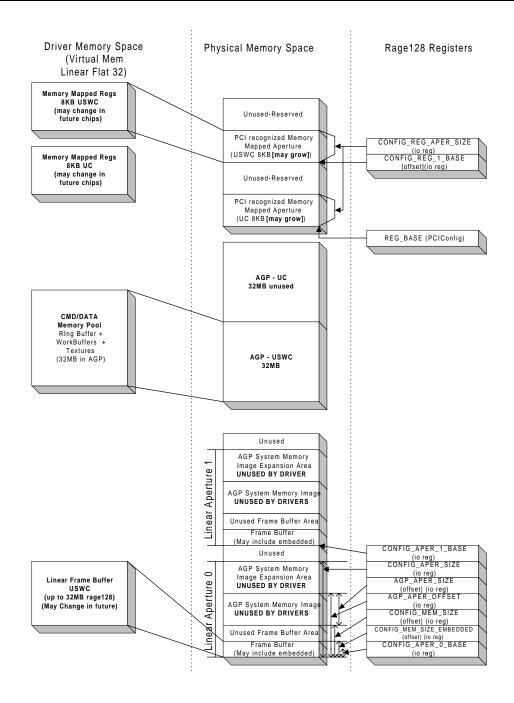

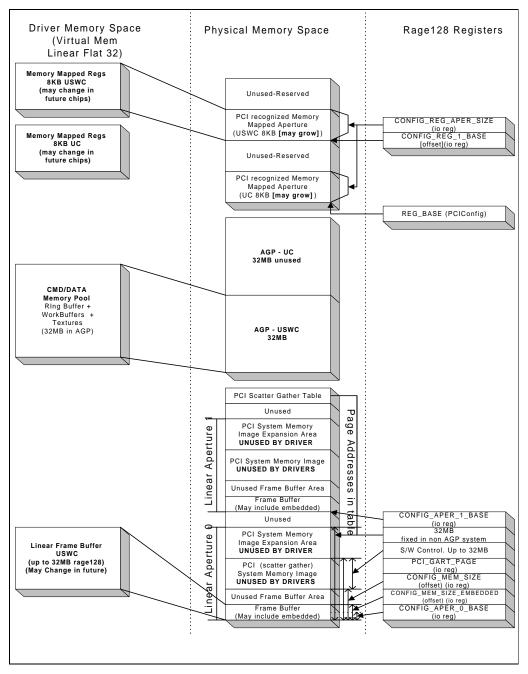

The following diagram shows the typical memory organization for the RAGE 128. Unless otherwise specified, all addresses in the register definition refer to a 64MB virtual address space.

The following groups are used:

- The first 32MB map to the frame buffer space.

- The next 32MB map to the AGP/PCI space, specifically: Address<sub>AGP</sub> = AGP\_base + (offset - 32MB) Address<sub>PCI</sub> = Physical address in BM\_GUI\_TABLE.

The following registers are used to point to the apertures:

- Registers **REG\_BASE** and **CONFIG\_REG\_1\_BASE** point to the register apertures.

- Registers **CONFIG\_APER\_0\_BASE** and **CONFIG\_APER\_1\_BASE** point to the video aperture.

Figure 2-5. Memory Map

### 2.6.1 VGA Memory Aperture

When enabled for VGA, the RAGE 128 claims the standard VGA resources. The bits contained in **GRPH\_ADRSEL** register determine the position and size of the VGA memory aperture. For most VGA graphics modes, the aperture is 128KB and starts at segment 0xA000.

# 2.6.2 Video BIOS

To relocate the RAGE 128's video BIOS, using the PCI configuration space. The system BIOS will normally shadow the entire BIOS image to the area starting at segment 0xC000 during system initialization.

## 2.6.3 Register Apertures

There are two memory-mapped register apertures in the RAGE 128. Each references the entire set of memory-mapped registers. Under the Intel architecture, one may be mapped for UnCached (UC) access, and the other for Write Combining (WC) access. WC is also uncached, but it is faster because it uses an out-of-order write buffer. The WC-mapped aperture may be used where speed is essential (e.g, when setting 3D states or setting up primitives). The UC-mapped aperture may be used when order is important (e.g, when initiating drawing operations).

Under the PowerMac architecture, the second aperture may be used for big-endian memory access.

#### Purpose

The register apertures contain all direct-accessed registers that are found in the RAGE 128, except for the VGA and PCI configuration registers. In addition, these registers also have the index/data pairs used for all indirectly accessed registers and memories.

#### Location

These registers are re-locatable. Base address of register aperture 0 is:

- Determined by the **REG\_BASE** register (found in the PCI configuration space), or

- Readable in the I/O register aperture using MM\_INDEX <= 0xF18 and reading MM\_DATA.

Base address of register aperture 1 is determined by **CONFIG\_REG\_1\_BASE**, which can be read in register aperture 0 once its base has been found as indicated above. Reading **CONFIG\_REG\_1\_BASE** is the only method of determining register aperture 1's location that is forward compatible with future generations of the hardware.

#### Size

The size will grow for future generations of the RAGE 128. The contents of the **CONFIG\_REG\_APER\_SIZE** register contains the sizes for each register aperture.

#### Memory Map

The following table shows the memory map.

| From   | То     | Description                                               |

|--------|--------|-----------------------------------------------------------|

| 0x0000 | 0x00FF | Non-GUI registers, also directly accessible in IOR space. |

| 0x0100 | 0x0EFF | Non-GUI registers.                                        |

| 0x0F00 | 0x0FFF | Read-only copy of PCI configuration space.                |

| 0x1000 | 0x13FF | CCE FIFO direct access.                                   |

| 0x1400 | 0x1FFF | GUI registers.                                            |

#### Table 2-10 Memory Map

## 2.6.4 Linear Memory Apertures

There are two copies of the linear memory aperture in the RAGE 128. Each copy is identical. The reason for two copies is to allow each to be independently marked as big-endian or little-endian in the PowerMac environment. For Wintel architectures, the second aperture may be used, but there is no valid reason to do so.

#### Purpose

The linear memory apertures allow access to the frame buffer memory, and for AGP systems to the AGP memory as seen by the RAGE 128.

#### Location

These apertures are re-locatable.

The **CONFIG\_APER\_0\_BASE** register determines the base address of linear aperture 0. The **CONFIG\_APER\_1\_BASE** register determines the base address of linear aperture 1. Both these registers can be read in any register aperture.

#### Size

The size of these registers will grow for future generations of the RAGE 128. The **CONFIG\_APER\_SIZE** register contains the size of each linear aperture.

#### **Frame Buffer**

The frame buffer image occupies the area in each aperture from offset 0 to CONFIG\_MEMSIZE-1.

If **CONFIG\_MEMSIZE\_EMBEDDED** is greater than zero, the RAGE 128 uses an on-chip memory for the first piece of the frame buffer. This embedded memory is included in the **CONFIG\_MEMSIZE** total. Currently, the RAGE 128 does not have any embedded memory. A future RAGE 128 model is planned to incorporate this embedded memory. The RAGE 128 supports up to 32MB of frame buffer memory.

# 2.6.5 AGP System Memory Image

Each linear aperture also contains an image of the AGP system memory as seen by the RAGE 128.

Typically, the host application would directly access the AGP system memory using the system processor. Since using this AGP image to access AGP memory generates an AGP slave and an AGP bus master cycle for each access (or group of accesses), it is highly inefficient; therefore, this method is not recommended.

Use this AGP image for debugging and allowing a method for flushing out pending AGP cycles still in the host chipset (before software directly accesses system memory).

The AGP image starts at offset **AGP\_APER\_OFFSET** in each linear aperture.

The **AGP\_APER\_SIZE** register contains the size of the AGP memory. This register is not a number, but an enumerated type that must be converted into a number (refer to the register definition).

The RAGE 128 supports up to 32MB of AGP memory.

# 2.6.6 RAGE 128 PCI GART

The RAGE 128 provides a mechanism for accessing system memory as AGP memory over the PCI bus. This mechanism allows up to 32MB of system memory on AGP cards, and up to 4MB on PCI cards, to be used as an AGP area using a scatter gather mechanism.

To use this feature, a 32KB table of page entries must be prepared and its physical base address must be written to the **PCI\_GART\_PAGE** register. The table must be 4KB aligned. Each table entry must contain the physical base address of a 4KB page allocated from system memory for the AGP area.

The PCI GART table is enabled by setting bit [0] of **PCI\_GART\_PAGE** to '0'. For AGP systems, this bit must be explicitly set to '1' during initialization to disable the PCI GART.

To force use of the PCI GART on AGP-capable systems, these additional steps are necessary:

- The BM\_CHUNK\_0\_VAL:BM\_PTR\_FORCE\_TO\_PCI field must be set to '1'.

- The BM\_CHUNK\_0\_VAL:BM\_RD\_FORCE\_TO\_PCI field must be set to '1'.

- The BM\_CHUNK\_0\_VAL:BM\_GLOBAL\_FORCE\_TO\_PCI field must be set to '1'.

Figure 2-6. AGP Memory Architecture - Software Layout

Figure 2-7. PCI Non-AGP Memory Architecture - Software Layouts

# 2.7 Display Mode and Mode Switching

A *display mode*, also referred to as *video mode*, defines the following parameters:

- The type of display content.

- The screen resolution.

- The color depth of the pixels.

This implies that setting up a display mode is dependent on the available video memory. Once an operating mode is determined, a display mode must also be set for the RAGE 128 according to the RAGE 128's capability and the available memory resource.

The RAGE 128 supports the following display modes in the VGA operating mode:

- *VGA-alphanumeric mode* (also known as the *text mode*) The text mode may further be classified into a number of sub-modes with variation in the size of character and in the color of text.

- VGA-graphics mode

This mode can also be further divided into sub-modes according to the screen resolution and the depth of color used to represent a pixel.

In the accelerator-operation mode, the RAGE 128 supports the graphics mode with screen resolutions (from 320x200 to 1600x1200 pixels), and with depths of color (8, 16, 24 and 32-bpp formats).

To switch from one display mode to another, call the BIOS service Set Display Mode (i.e. function AL = 1), and/or Coprocessor CRTC Parameters (i.e. function AL = 0).

# 2.8 Engine Discipline

In the accelerator-operation mode, the RAGE 128's GUI engine may use the PIO drawing mode or the CCE drawing mode.

If switching between these two operation modes is not handled properly, the RAGE 128 may hang (i.e. stop operating). To avoid hanging the RAGE 128, follow these pointers:

- To safely switch from one mode to another, make sure the Command FIFO buffer is empty and it is in the idle state. This requires the program to check that the 31<sup>st</sup> bit of register **GUI\_STAT** is set to zero.

- When the RAGE 128 operates in the PIO drawing mode, the program must check if there are sufficient entries in the Command FIFO buffer before writing any data to it.

# 2.9 BIOS Services

A number of BIOS services are available. These services help to avoid problems of incorrectly setting up the RAGE 128 or configuring the display mode of the system.

For details about *BIOS Services*, see the *Appendix for the "BIOS Function Calls"*, on page A-1.

This page intentionally left blank.

# **Chapter 3** Accelerator Operation Mode

# 3.1 Scope

This chapter contains information about setting up the RAGE 128 for accelerator-operation mode. The intended audience for this information is X-type OS driver developers.

This chapter shows how to detect the RAGE 128 without using the BIOS functions. The majority of the necessary information can be retrieved from the PCI Configuration Space, which is set at POST.

The following information can be retrieved through the PCI Configuration Space:

- PCI Vendor ID

- Device ID

- Revision ID

- BIOS segment

- Base address of the register

- Memory and I/O apertures

For host applications to access the registers and memories through the apertures, the initialization program needs to configure the RAGE 128 for accelerator-operation mode, and convert the aperture addresses from physical space to linear space.

The initialization stage consists of the following four major steps:

- Step 1: Detecting the RAGE 128.

- Step 2: Obtaining the configuration information about the physical and linear (i.e. virtual) addresses of apertures.

- Step 3: Setting up a display mode.

- Step 4: Initializing the GUI engine.

# 3.2 Step 1: Detect the RAGE 128

This step determines the following:

- The presence of a RAGE 128 within the system

- The various aperture addresses (memory, register, and I/O).

To determine much of this information, use the PCI configuration space. For the purposes of this document, the following lists several assumptions:

- The system uses the PCI host bus (since the RAGE 128 is only available in PCI and AGP bus types).

- The OS being used provides an interface for querying the PCI configuration space. If this is not the case, the programmer must gain access to this information.

# 3.2.1 Using the PCI Configuration Space

To use the PCI configuration space, follow these steps:

- 1. Detect if a device is installed that contains the ATI PCI Vendor ID (0x1002). As per the PCI specification, offset'0' of the configuration space for a given device contains the PCI Vendor ID.

- 2. After identifying a device that has the ATI PCI Vendor ID, determine the Device ID.

- **3.** Check to if the device ID matches the list of known RAGE 128 device IDs. The current list of RAGE 128 device IDs are as follows:

| Package ID | Device ID | Description         |

|------------|-----------|---------------------|

| RE         | 0x5245    | 312pin, PCI 33 only |

| RF         | 0x5246    | 312pin, AGP 1X & 2X |

| RK         | 0x524B    | 256pin, PCI 33 only |

| RL         | 0x524C    | 256pin, AGP 1X & 2X |

Table 3-1 RAGE 128 Device IDs

4. Note that the Device ID is located at offset 0x02 of the configuration space.

- **5.** After obtaining the value of the Device ID, compare it against the above list. If there is a match, we can continue. Otherwise, we have two options:

- Return an error, indicating that a RAGE 128 device was not found -OR-

- Scan the BIOS segment to see if the 'R128' signature string is found (note: a way to detect a RAGE 128 revision that may not be in the list). This protects against a driver not detecting new or revised RAGE 128s. However, this also has the potential for problems in that the new revision may require some modifications to the driver to work properly. This point should be considered before implementation.

For the latest list of Device IDs for the RAGE 128, contact Developer Relations at ATI (www.atitech.com).

## 3.2.2 Scanning the BIOS Segment

By scanning the BIOS segment, the following information can be found:

- ROM ID The ROM ID is defined as 'AA55' in the first two bytes of the BIOS segment.

- ATI product signature The ATI product signature is '761295520'.

- RAGE 128 string The RAGE 128 string is 'R128'.

For a successful installation of the RAGE 128, all three of these items must be present. They should all be present within the first 512 bytes of the BIOS segment.

## 3.2.3 Scratch Register Test

To confirm the presence of a RAGE 128 board on the PCI bus, perform a read-and-write test on register **BIOS\_0\_SCRATCH**. Perform this test through the I/O port. Use the following steps:

- 1. Read and save the contents of register **BIOS\_0\_SCRATCH**.

- 2. Write the value (e.g. 0x55555555) to BIOS\_0\_SCRATCH.

- **3.** Read back **BIOS\_0\_SCRATCH**. If the value is not the same as what was written, a RAGE 128 is not present.

- **4.** Repeat steps 2 and 3, using the compliment of the previous value (e.g. **OXAAAAAAA**).

- 5. Restore the saved value of **BIOS\_0\_SCRATCH**.

# 3.3 Step 2: Obtain the Configuration Information

After locating the PCI configuration space for a RAGE 128, some additional configuration information can be retrieved, such as:

- Memory aperture base address (PCI configuration space offset 0x10).

- Register aperture base address (PCI configuration space offset 0x18).

- I/O base address (PCI configuration space offset 0x14).

- BIOS segment address (PCI configuration space offset 0x30).

The memory aperture base address value at offset 0x10 within the PCI configuration space is in bits [31:26] of its DWORD. Therefore, to isolate the proper bits, the value should be logically ANDed with 0xFC000000.

For the I/O base aperture, the actual value is within bits [31:8] of its DWORD (at offset 0x14). Therefore, to isolate the proper bits, the value should be logically ANDed with 0xFFFFFF00.

The register aperture base value resides in bits [31:14] of its DWORD (at offset 0x18). Therefore, to isolate the proper bits, the value should be logically ANDed with 0xFFFFC000.

The BIOS segment, at offset 0x30, is in the upper WORD of this value (bits [31:17]), then shifted right one bit.

After obtaining these physical memory addresses for the memory and register apertures, convert them to virtual or linear addresses, so that the host application may use them.

#### Example Code: Converting the physical addresses to a usable virtual address

```

DWORD phys_to_virt (DWORD physical, DWORD size)

{

union REGS r;

struct SREGS sr;

DWORD retval=0;

memset (&r, 0, sizeof (r));

memset (&sr, 0, sizeof (sr));

r.w.ax = 0x0800;

r.w.bx = physical >> 16;

r.w.cx = physical & 0xFFFF;

r.w.si = size >> 16;

r.w.di = size & 0xFFFF;

```

```

int386x (0x31, &r, &r, &sr);

if ((r.w.cflag & INTR_CF) == 0)

{

retval = (long) (((long) r.w.bx << 16) | r.w.cx);

} // if

return (retval);

} // phys_to_virt

```

At this point, you have successfully detected that a RAGE 128-based graphics adapter is installed.

The following lists the configuration information about the adapter has been revealed:

- ASIC version (Device ID)

- BIOS segment

- Memory aperture address (both physical and virtual)

- Register aperture address (both physical and virtual)

- I/O base address

This gives sufficient information to begin the next step: setting up a display mode, and initializing the graphics engine (GUI).

# 3.4 Step 3: Set a Display Mode

This section covers how to set a display mode. To select a display mode, use one of the following methods:

- Use the BIOS function (i.e. the easy method).

- Manually set up the display mode (i.e. the hard method).

### Easy Method

To set the display mode using an easy method, use the BIOS function 0x00. Supply parameters for the mode number and the color depth in the appropriate CPU registers. Then, call the function. A variant of this method also allows you to pass a CRT parameter table to supply custom CRT values, even custom resolutions.

### **Difficult Method**

To set the display mode using a hard method, manually program the PLL and CRT to achieve the desired mode. Typically, protected-mode operating systems (i.e. usually X type OSs) must use this method (since they are unable to execute the BIOS functions within their OS). If the programmer has any possibility of using the BIOS to set the mode, this would be much preferred.

# 3.4.1 Using the BIOS Function

The RAGE 128 can be set up in a particular display mode by calling the extended BIOS function 00h, **Set Display Mode**. Here are the inputs required for this function:

Table 3-2 Inputs for the Set Display Mode BIOS Function

| Code    | Purpose                                                                                                                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| di      | Display Device Mask.<br>This determines what display will be affected by this call. Default is '0', which<br>affects all displays. |

| cl[0:3] | Color depth.                                                                                                                       |

| ch      | Resolution.                                                                                                                        |

| dx:bx   | Pointer to parameter table (if we choose to set the mode from a parameter table).                                                  |